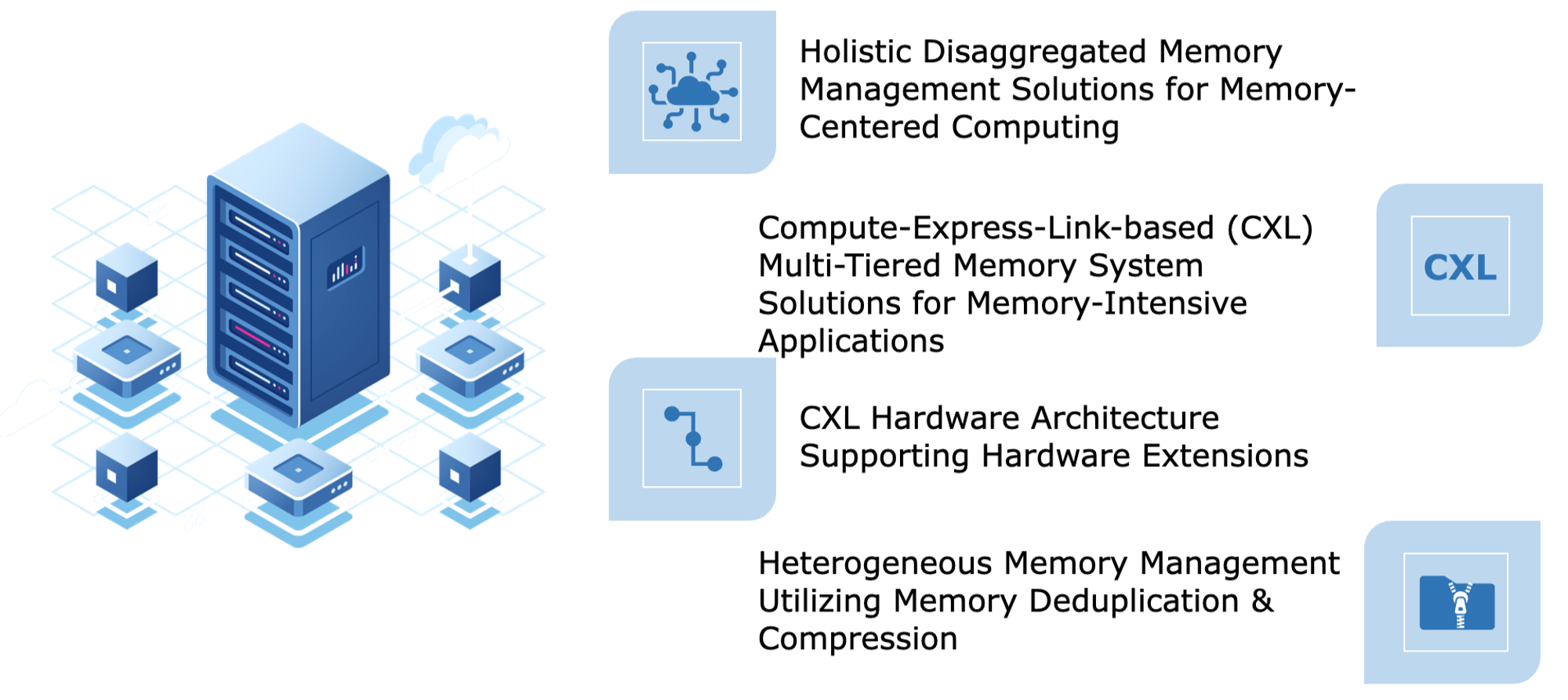

We are committed to advancing memory technologies and their associated architectural solutions. A key focus of our work is the development of holistic, disaggregated memory management solutions optimized for memory-centric computing paradigms. By addressing the challenges of distributed memory resources, we aim to design cohesive strategies that ensure efficient memory utilization and seamless data access across interconnected memory units. Additionally, we are innovating Compute Express Link (CXL)-based multi-tiered memory systems for memory-intensive applications. By integrating CXL technology, we aim to create tiered memory architectures that combine high-speed and high-capacity memory units to meet the demands of data-intensive workloads. Our research also enhances the CXL hardware architecture, focusing on accommodating hardware extensions. By designing flexible and extensible hardware frameworks, we seek to integrate novel memory technologies in a way that supports future scalability and innovation. Furthermore, we are exploring heterogeneous memory management, employing techniques such as memory deduplication and compression. These methods aim to optimize memory utilization by reducing redundancy and maximizing the effective capacity of memory resources. Our objective is to shape the future of memory systems and architectures by providing innovative solutions that empower memory-intensive computing, enable efficient data processing, and pave the way for more sophisticated and capable memory technologies.

Next-Generation Memory Systems & Architecture

Publications

- (Conference) ARIADNE: Adaptive UVM Management for Efficient GPU Memory Oversubscription

- (Conference) Para-ksm: Parallelized Memory Deduplication with Data Streaming Accelerators

- (Journal) SAFE: Sharing-aware Prefetching for Efficient GPU Memory Management with Unified Virtual Memory

- (Journal) RoPIM: A Processing-in-Memory Architecture for Accelerating Rotary Positional Embedding in Transformer Models

- (Journal) Cooperative Memory Deduplication with Intel® Data Streaming Accelerator

- (Journal) NoHammer: Preventing Row Hammer With Last-Level Cache Management

- (Journal) T-CAT: Dynamic Cache Allocation for Tiered Memory Systems With Memory Interleaving

- (Conference) IDIO: Network-Driven, Inbound Network Data Orchestration on Server Processors

- (Conference) InnerSP: A Memory Efficient Sparse Matrix Multiplication Accelerator with Locality-Aware Inner Product Processing

- (Conference) GreenDIMM: OS-assisted DRAM Power Management for DRAM with a Sub-array Granularity Power-Down State

- (Journal) IDIO: Orchestrating Inbound Network Data on Server Processors

- (Patent) Method and Apparatus for detecting cache side channel attack using trusted execution environment

- (Patent) Device and Method for managing DRAM power

- (Journal) Exploiting OS-Level Memory Offlining for DRAM Power Management

- (Conference) Application-Transparent Near-Memory Processing Architecture with Memory Channel Network

- (Journal) Virtual Snooping Coherence for Multi-Core Virtualized Systems

- (Conference) vCache: Architectural support for transparent and isolated virtual LLCs in virtualized environments

- (Journal) vCache: Providing a Transparent View of the LLC in Virtualized Environments

- (Journal) Subspace Snooping: Exploiting Temporal Sharing Stability for Snoop Reduction

- (Conference) Virtual Snooping: Filtering Snoops in Virtualized Multi-cores

- (Conference) Subspace Snooping: Filtering Snoops with Operating System Support